Chip bán dẫn là gì? Quy trình sản xuất chip bán dẫn

Chip bán dẫn là vật liệu quan trọng không thể thiếu trong ngành sản xuất thiết bị công nghệ và được sử dụng rộng rãi.

Vậy chip bán dẫn là gì? Quy trình sản xuất chip bán dẫn diễn ra như thế nào? Cùng Thiết bị phòng sạch VCR tìm hiểu thông tin này qua bài viết bên dưới.

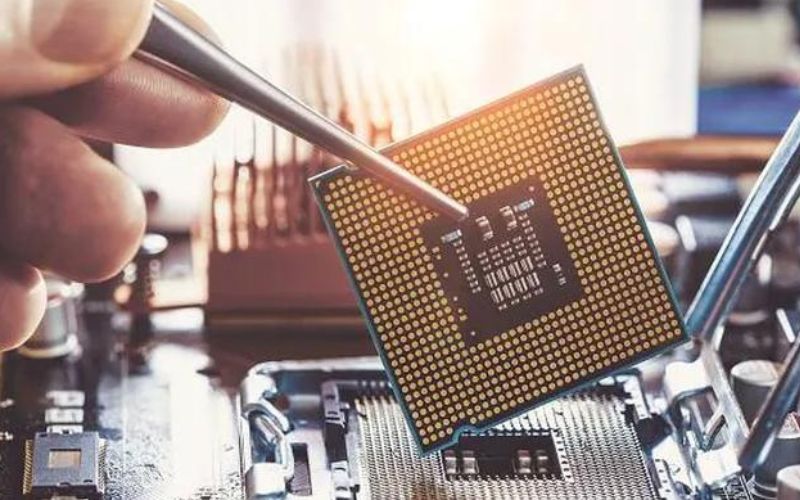

1. Chip bán dẫn là gì? Cấu tạo chip bán dẫn

Chip bán dẫn còn có tên khác là ic (viết tắt của integrated circuit), là thành phần điện tử được tạo ra trên một lớp bán dẫn (thường là silic) để thực hiện một số chức năng điện tử.

Cấu tạo chip bán dẫn gồm nhiều lớp chất bán dẫn đặt lên nhau, chúng bao gồm các thành phần điện tử như resistor, capacitor, diode, transistor. Các linh kiện này kết nối với nhau thông qua đường dẫn trên bề mặt chip, tạo thành mạch điện tử hoàn chỉnh.

Chức năng của chip bán dẫn khá đa dạng, chẳng hạn như: Lưu trữ thông tin, xử lý dữ liệu, đảm bảo giao tiếp trên mạng hoặc điều khiển các thiết bị khác nhau. Chip bán dẫn thường được sử dụng trong các thiết bị điện tử như: Máy chơi game, máy tính bảng, điện thoại di động, máy tính, thiết bị y tế,...

Nhà sản xuất đã ứng dụng công nghệ quy trình chất bán dẫn để thiết kế và sản xuất chip bán dẫn, chúng đóng vai trò quan trọng trong sự phát triển của công nghệ thông tin và điện tử.

Tìm hiểu thêm:

2. Chi tiết quy trình sản xuất chip bán dẫn

System design

Phần thiết kế này rất quan trọng và thường được thực hiện bởi trưởng dự án. Người thiết kế cần lý giải 100% hệ thống sắp thiết kế, bao gồm các nội dung: Chọn kiểu chip nào? Tại sao lại chọn? Kích cỡ của chip? Số lượng bóng bán dẫn được tích hợp trên chip? Sử dụng công nghệ nào để sản xuất chip? Chip được sản xuất và kiểm tra ở đâu? Thời điểm phù hợp để phân phối ra thị trường?.

Bên cạnh đó, cần phải hiểu rõ nguyên lý hoạt động của hệ thống, tốc độ xử lý, các đặc điểm về công nghệ, cách bố trí Pins, mức tiêu thụ năng lượng, các điều kiện vật lý, các lược đồ khối.

Các công đoạn thiết kế trong system design diễn ra tự nhiên và không có bất kỳ sự hỗ trợ từ công cụ chuyên dụng. Sau khi hoàn thành bản thiết kế hệ thống, trưởng dự án sẽ phân nhỏ công việc cho từng đội thiết kế như đội CPU, đội Peripheral, đội Bus,...

Function design

Bước kế tiếp của system design là function design. Ví dụ đối với đội CPU, người quyết định SPEC (Standard Performance Evaluation Corporation) chính là team leader. Chi tiết của CPU dựa trên yêu cầu hệ thống từ trưởng dự án. Hàng tuần, các cuộc design review sẽ diễn ra giữa trưởng dự án và team leader. Sau nhiều cuộc họp, tiến hành thống nhất bản SPEC chi tiết chi tiết cho CPU dưới dạng document (pdf, word) với các loại bảng biểu khác nhau.

Team leader chia nhỏ công việc cho tất cả thành viên trong đội, chẳng hạn như một người đảm nhận Decoder, người khác đảm nhận phần ALU,... Các thành viên sẽ sử dụng ngôn ngữ thiết kế phần cứng (Verilog-HDL, VHDL.System-C,...) nhằm mục đích thực hiện hóa chức năng logic. Mức thiết kế này thường được gọi là thiết kế mức RTL (Register Transfer Level), nghĩa là chỉ chú trọng vào chức năng của mạch điện mà không cần quan tâm đến chi tiết của mạch.

Tương tự, với các module khác: Bus, peripherals,... Các module trên được ghép với nhau để cấu thành SoC hoàn chỉnh, bao gồm: peripherals, bus, system,.. SoC chính là kết quả của Function Design.

Synthesis-place-router

Công đoạn này được thực hiện nhằm chuyển những RTLs đã thiết kế xuống mức thiết kế thấp hơn. Các chức năng mức trừu tượng cao (RTL) được hoán đổi thành quan hệ logic như MUX, NOR. Các tool chuyên dụng như Design Compiler của hãng Synopsys, XST của hãng Xilinx,... sẽ thực hiện nhiệm vụ này. Tùy theo thư viện và Synthesis Tool sẽ cho ra kết quả khác nhau. Thư viện ở đây là bộ các “macro” và “linh kiện” được cung cấp bởi nhà sản xuất.

Kết quả đạt được của bước Synthesis là các Nest - list cấu trúc theo một tiêu chuẩn nhất định, thường là EDIF (Electronic Degisn Interchance Format). Nest - list đánh dấu sự hoàn thành thiết kế SoC ở mức độ “thượng lưu”.

Layout design

Đây là khởi đầu cho thiết kế ở mức “hạ lưu”, thường được thực hiện bởi các chuyên gia sản xuất bản dẫn. Để chuyển nest - list sang kiểu data cho layout, người ta thường sử dụng công cụ CAD. Lúc này, nest - list trở thành bản vẽ bố trí các resistor, capacitor, transistor. Công đoạn này cần tuân thủ nghiêm ngặt các quy luật trong thiết kế (design rule).

Mask pattern design

Công đoạn này thực hiện tương tự với artwork trong thiết kế bản in. Các bộ Mask sẽ được tạo ra dưới dạng data đặc biệt. Sau đó, các Mask data được gửi cho nhà sản xuất Mask để nhận bộ Mask kim loại, sử dụng cho các công đoạn sản xuất kế tiếp.

Sản xuất mask

Trong công nghệ sản xuất mask, thường dùng tia điện tử (EB - Electron Beam). Các điện tử với năng lượng lớn sẽ được vuốt thành chùm và chiếu vào lớp film Crom đổ trên bề mặt tấm thủy tinh. Với các phần Cr không bị che bởi Mask sẽ bị phá hủy, kết quả thu được là phần Cr không bị electron chiếu vào và trở thành Mask thực thụ.

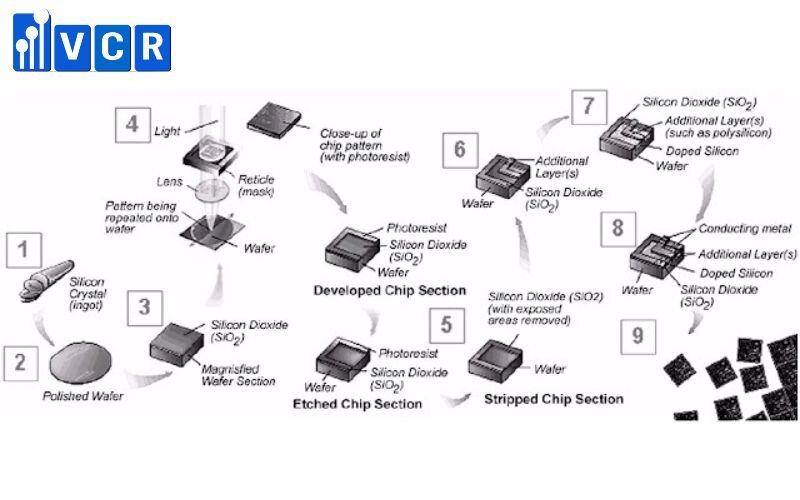

Chuẩn bị wafer

Thực hiện công đoạn này nhằm mục đích tinh chế cát (SiO2) thành Silic nguyên chất. Sau đó, sử dụng các nguyên tố nhóm 3 hoặc 5 để cho vào Silic nguyên chất. Ví dụ, pha P sẽ ra wafer loại n, pha B sẽ ra wafer loại p. Silicon được cắt thành các tấm tròn với đường kính từ 200mm - 300mm.

Quá trình xử lý wafer

Công đoạn tiếp theo trong quy trình sản xuất chip điện tử là xử lý wafer. Tất cả được thực hiện trong môi trường sạch (ultra clean room). Quá trình này gồm các bước:

- Rửa (wet process): Sử dụng dung dịch hóa học để làm sạch wafer.

- Oxy hóa (oxidation): Trên bề mặt wafer, tiến hành tạo SiO2. Lớp SiO2 mỏng từ 1 - 2 nanomet trở thành gate của transistor.

- CVD (Chemical Vapor Deposition): Sử dụng phương pháp hóa học để tạo lớp film mỏng trên bề mặt wafer.

- Cấy Ion (Ion implantation): Sử dụng Ion năng lượng cao bắn trên bề mặt Si nhằm mục đích thay đổi nồng độ tạp chất trong Si.

- Cắt (etching): Mục đích thực hiện bước này để loại bỏ SiO2 không cần thiết, gồm 2 loại: Dry-etching dùng plasma để cắt SiO2 ra khỏi bề mặt Si và wet-etching sử dụng axit HF loãng để hòa tan SiO2.

- Photolithography: Là phương pháp xử lý quang học để transfer mask pattern lên bề mặt wafer. Trên bề mặt wafer được phết lớp dung dịch resist có độ dày khoảng 0.5um. Ánh sáng chiều lên mask sẽ đi qua và làm mềm resist. Sau khi dùng dung dịch đặc biệt để rửa, phần resist không bị ánh sáng chiếu vào và tồn tại trên wafer như mask.

- Sputtering: Tiến hành phủ các nguyên tử kim loại (Al, Cu) lên bề mặt wafer. Ion Ar+ trong môi trường plasma sẽ bắn các target kim loại như Cu, W, Al. Lúc này, các nguyên tử bật ra và bám trên bề mặt wafer. Phần bị phủ trở thành dây dẫn và kết nối các transistor với nhau.

- Annealing: Đây là công đoạn xử lý nhiệt nhằm mục đích giúp các liên kết chưa hoàn chỉnh của Si liên kết với H+, từ đó giảm trap năng lượng tại bề mặt SiO2 và Si.

- CMP (Chemical Mechanical Polishing): Sử dụng phương pháp cơ hóa để làm phẳng bề mặt. Đây là kỹ thuật mới có tác dụng hỗ trợ các công đoạn xử lý như photolithography, etching etc.

Kiểm tra, đóng gói và xuất xưởng

Kiểm tra, đóng gói và xuất xưởng là công đoạn có mặt trong hầu hết quy trình sản xuất chất bán dẫn. Tùy thuộc vào mức độ phức tạp của chip, công đoạn này sẽ được lặp đi lặp lại nhiều lần và được cắt rời (một tấm wafer 300mm được cắt rời thành 90 con chip Pentium IV).

Bên cạnh đó, còn có thêm các công đoạn xử lý khác: Bonding (nối ra các pins, dùng chỉ đồng hoặc mạ vàng), grinding (thực hiện mài mỏng phần mặt dưới của chip), marking (ghi thông tin hãng sản xuất), mold (phủ lớp cách điện).

3. Một số thiết bị để sản xuất

- Thiết bị tạo mặt phẳng cho chip bán dẫn.

- Thiết bị chụp ảnh.

- Thiết bị ánh sáng.

- Thiết bị phủ mạ và ets.

- Thiết bị đo lường.

- Thiết bị phân tích.

Tóm lại, chip bán dẫn đã làm thay đổi đời sống hiện nay bằng cách tạo ra nhiều dịch vụ và sản phẩm mới, cải thiện hiệu suất cho nhiều lĩnh vực.

Bài viết trên là chia sẻ của VCR liên quan đến quy trình sản xuất chip bán dẫn. Mong rằng, bạn đọc sẽ thu thập được kiến thức hữu ích và áp dụng vào thực tế thành công.

Xem thêm video: